# Small Signal Diode

#### **Features**

- ♦Meet IEC61000-4-2 (ESD) ±15kV (air), ±8kV (contact)

- ♦Meet IEC61000-4-4 (EFT) rating. 40A (5/50ήs)

- ♦Protects one birectional I/O line

- ♦Working Voltage: 5V

- ♦Pb free version, RoHS compliant, and Halogen free

#### **Mechanical Data**

- ♦Case : SOD-523F flat lead small outline plastic package

- ◆Terminal: Matte tin plated, lead free., solderable per MIL-STD-202, Method 208 guaranteed

- ♦High temperature soldering guaranteed: 260°C/10s

- ♦Mounting position: Any

- ♦Weight :2 mg (approximately)

- ♦Marking Code : DT

# **Applications**

- ♦ Cell Phone Handsets and Accessories

- ♦Notebooks, Desktops, and Servers

- ♦Keypads, Side Keys, USB 2.0, LCD Displays

- ♦Portable Instrumentation

- ♦Microprocessor based equipment

#### **Ordering Information**

| Part No. | Package  | Packing      | Packing Code | Marking |

|----------|----------|--------------|--------------|---------|

| TESDD5V0 | SOD-523F | 3K / 7" Reel | RKG          | DT      |

### **Maximum Ratings and Electrical Characteristics**

Rating at 25°C ambient temperature unless otherwise specified.

#### **Maximum Ratings**

| Type Number                                                    | Symbol          | Value        | Units |

|----------------------------------------------------------------|-----------------|--------------|-------|

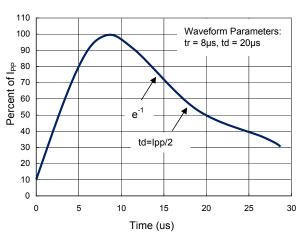

| Peak Pulse Power (tp=8/20µs waveform)                          | P <sub>PP</sub> | 100          | W     |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | Vesd            | ±15<br>±8    | KV    |

| Junction and Storage Temperature Range                         | TJ, Tstg        | -55 to + 150 | °C    |

#### **Electrical Characteristics**

| Type Number               |                              | Symbol     | Min  | Max   | Units |

|---------------------------|------------------------------|------------|------|-------|-------|

| Reverse Stand-Off Voltage |                              | $V_{RWM}$  | -    | 5     | V     |

| Reverse Breakdown Volta   | I <sub>R</sub> = 1mA         | $V_{(BR)}$ | 6    | -     | V     |

| Reverse Leakage Curren    | V <sub>R</sub> = 5V          | IR         | -    | 1     | uA    |

| Clamping Voltage          | I <sub>PP</sub> = 1A         | Vc         | -    | 9.8   | V     |

|                           | I <sub>PP</sub> = 3A         | VC         | -    | 15    | ]     |

| Junction Capacitance      | V <sub>R</sub> =0V, f=1.0MHz | Сı         | 13 ( | Тур.) | pF    |

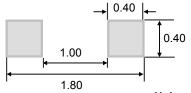

Notes: 1. The suggested land pattern dimensions have been provided for reference only, as actual pad layouts may vary despending on application.

# TESDD5V0 Bi-directional ESD Protection Diode

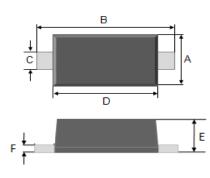

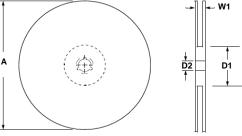

#### **SOD-523F**

| Dimensions | Unit (mm) |      | Unit (inch) |       |

|------------|-----------|------|-------------|-------|

|            | Min       | Max  | Min         | Max   |

| Α          | 0.70      | 0.90 | 0.028       | 0.035 |

| В          | 1.50      | 1.70 | 0.059       | 0.067 |

| С          | 0.25      | 0.35 | 0.010       | 0.014 |

| D          | 1.10      | 1.30 | 0.043       | 0.051 |

| E          | 0.60      | 0.70 | 0.024       | 0.028 |

| F          | 0.10      | 0.14 | 0.004       | 0.006 |

# Pin Configutation

#### **Suggested PAD Layout**

Unit : mm

#### **Small Signal Diode**

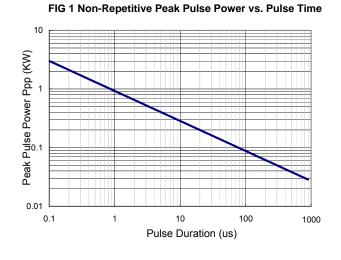

#### **Rating and Characteristic Curves**

FIG 2 Pulse Waveform

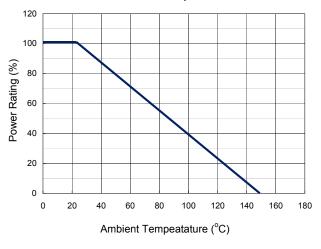

FIG 3 Admissible Power Dissipation Curve

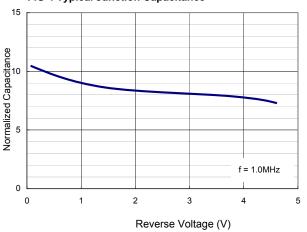

**FIG 4 Typical Junction Capacitance**

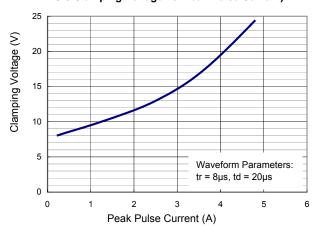

FIG 5 Clamping Voltage vs. Peak Pulse Current)

#### **Small Signal Diode**

#### **Applications Information**

- ♦Designed to protect one data, I/O, or power supply line.

- ♦Designed to protect sensitive electronics from damage or latch-up due to ESD

- ♦Designed to replace multilayer varistors (MLVs) in portable applications

- ♦Offers superior electrical characteristics such as lower clamping voltage and no device degradation when compared to MLVs

- ♦The combination of small size and high ESD surge capability makes them ideal for use in portable applications.

#### **Circuit Board Layout Recommendations**

Good circuit board layout is critical for the suppression of ESD induced transients.

- ♦ Place the ESD Protection Diode near the input terminals or connectors to restrict transient coupling.

- ♦ Minimize the path length between the ESD Protection Diode and the protected line.

- Minimize all conductive loops including power and ground loops.

- ♦The ESD transient return path to ground should be kept as short as possible.

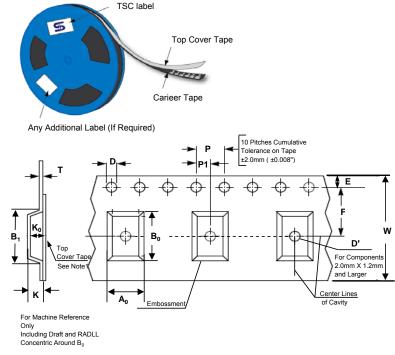

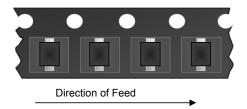

## Tape & Reel specification

| Item                   | Symbol | Dimension<br>(mm) |  |

|------------------------|--------|-------------------|--|

| Carrier depth          | K      | 2.40 Max.         |  |

| Sprocket hole          | D      | 1.50 +0.10        |  |

| Reel outside diameter  | Α      | 178 ± 1           |  |

| Reel inner diameter    | D1     | 50 Min.           |  |

| Feed hole width        | D2     | 13.0 ± 0.5        |  |

| Sprocke hole position  | E      | 1.75 ±0.10        |  |

| Punch hole position    | F      | 3.50 ±0.05        |  |

| Sprocke hole pitch     | P0     | 4.00 ±0.10        |  |

| Embossment center      | P1     | 2.00 ±0.10        |  |

| Overall tape thickness | Т      | 0.6 Max.          |  |

| Tape width             | W      | 8.30 Max.         |  |

| Reel width             | W1     | 14.4 Max.         |  |

Note 1:  $A_0$ ,  $B_0$ , and  $K_0$  are determined by component size. The clearance between the components and the cavity must be within 0.05 mm min. to 0.5 mm max. The component cannot rote more than 100 within the determined cavity.

Note 2: If B1 exceeds 4.2 mm(0.165") for 8 mm embossed tape, the tape may not feed through all tape feeders.